#### **ABSTRACT**

Development and Implementation of Real-time Distributed Network with the CAN Protocol

#### Walter D. Ford

Mentor: Ian A. Gravagne, Ph.D.

One of the most interesting applications of a new field of mathematics called dynamic equations on time scales is the modeling, analysis and design of distributed control networks. This thesis documents the development of a scalable, real-time test bed on which to test new time scale-based theories. The Controller Area Network (CAN) protocol is used as the communication backbone. A general description of CAN and reasons for its selection are included. A general purpose computational node is implemented on a desktop computer running the QNX real-time operating system. QNX development entailed writing a driver for an SJA1000-based CAN controller. Charmed Labs' Xport and the Gameboy Advance (GBA) are used for the network of embedded nodes. Development for the GBA-Xport combination involved interfacing an OpenCores.org CAN core to the Xport's bus on an FPGA in Verilog and writing a driver class. Appendices include the code and code documentation.

# Development and Implementation of Real-time Distributed Network with the CAN Protocol

by

Walter D. Ford, B.S.E.C.E.

A Thesis

Approved by the Department of Electrical and Computer Engineering

James B. Farison, Ph.D., Chairperson

Submitted to the Graduate Faculty of Baylor University in Partial Fulfillment of the Requirements for the Degree

ot

Master of Science in Electrical and Computer Engineering

Approved by the Thesis Committee

Ian A. Gravagne, Ph.D. Chairperson

Steven R. Eisenbarth, Ph.D.

Glenn A. Miller, Ph.D.

Accepted by the Graduate School

December 2005

$\frac{1}{2}$

J. Larry Lyon, Ph.D., Dean

# TABLE OF CONTENTS

| LIST OF FIGURES                                   | :  |

|---------------------------------------------------|----|

| LIST OF FIGURES                                   |    |

|                                                   |    |

| DEDICATION                                        |    |

| CHAPTER ONE                                       | 1  |

| Introduction                                      | 1  |

| CHAPTER TWO                                       | 4  |

| General Description of CAN                        | 10 |

| CHAPTER THREE                                     | 10 |

| Technology Used in CAN Bus Implementation         | 10 |

| QNX Real-Time Operating System                    |    |

| Scalable Architecture                             |    |

| Resource Managers                                 |    |

| Interrupts                                        |    |

| Arcom AIM104-CAN Controller Board                 |    |

| Nintendo Gameboy Advance SP                       |    |

| CharmedLabs Xport 2.0 and XRC                     |    |

| Xilinx Spartan II FPGA                            |    |

| Xport Robot Controller                            |    |

| CharmedLabs Open-Source Libraries                 |    |

| OpenCores.org CAN Core                            |    |

| Microchip MCP2551 CAN Transceiver                 |    |

| CHAPTER FOUR                                      | 22 |

| QNX Driver Development                            |    |

| SJA1000 Access Functions                          |    |

| Interrupt Handler                                 |    |

| I/O and Connect Functions                         |    |

| can4qnx Resource Manager                          |    |

| CHAPTER FIVE                                      | 27 |

| Xport CAN Controller Development                  |    |

| Bus Description and Behaviour                     |    |

| GBA to OpenCores.org CAN Controller Bus Interface |    |

| CAN Core-GBA Interrupt Interface                  |    |

| Hardware Reset Register                           |    |

| CAN Transceiver                                   |    |

| CAN Core Library Class                            |    |

| Conclusion                                        | 35 |

| APPENDIX A                                        | 37 |

| Appendix Documenting can4qnx Code                 |    |

| QNX SJA1000 Access Functions                      |    |

| Interrupt Handler                                 |    |

| I/O and Connect Functions                         | 41 |

| can4qnx Resource Manager            | 44  |

|-------------------------------------|-----|

| Miscellaneous Files and Functions   | 45  |

| APPENDIX B                          | 48  |

| Appendix Documenting CCanCore Code  |     |

| CAN Core Class Access Functions     | 48  |

| Interrupt Handler                   | 52  |

| Other Files                         |     |

| APPENDIX C                          | 55  |

| Appendix Documenting Verilog Source |     |

| CAN Interface Inputs and Outputs    | 55  |

| GBA Inputs and Ouptuts              |     |

| CartData to address Addr            | 55  |

| CAN Transceiver Inputs and Ouptuts  | 55  |

| Troubleshooting Outputs             |     |

| CAN Interface Module Summary        |     |

| OpenCores.org CAN Core              | 56  |

| CAN Core Reset                      | 57  |

| IRQ Interface                       | 57  |

| Bus Interface Combinational Logic   | 57  |

| Bus Interface State Machine         |     |

| Xport Primary Module                | 58  |

| CAN Controller Module               | 58  |

| Other Modules                       | 58  |

| APPENDIX D                          | 60  |

| can4qnx Source Code                 |     |

| can_close.c                         | 60  |

| can_defs.h                          | 60  |

| can_devctl.c                        | 64  |

| can_error.c                         | 68  |

| can_open.c                          | 69  |

| can_read.c                          | 69  |

| can_resmgr.c                        | 70  |

| can_sja1000.h                       | 72  |

| can_sja1000funcs.c                  | 77  |

| can_sysctl.c                        | 86  |

| can_util.c                          | 87  |

| can_write.c                         | 90  |

| can4qnx.h                           | 91  |

| APPENDIX E                          | 95  |

| Verilog Source Code                 |     |

| CAN.v                               | 95  |

| can_bot.v                           | 97  |

| APPENDIX F                          | 101 |

| CCanCore Source Code                |     |

| ccancore.cxx                        | 101 |

| ccancore.h                          | 113 |

| gbaCAN.h     | 114 |

|--------------|-----|

| BIBLIOGRAPHY | 120 |

# LIST OF FIGURES

| Figure 1: CAN Nodes                      | . 5  |

|------------------------------------------|------|

| Figure 2: Differential CAN Signal        | . 6  |

| Figure 3: TTL to Differential CAN        | . 19 |

| Figure 4: GBA-Xport Block Diagram        | . 20 |

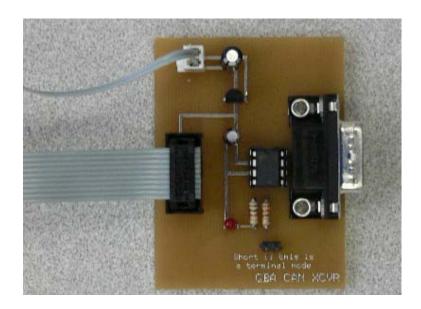

| Figure 5: CAN Node Picture               | . 21 |

| Figure 6: Resource Manager Block Diagram | . 26 |

| Figure 7: Write to CAN Address.          | . 28 |

| Figure 8: Read from CAN Address          | . 28 |

| Figure 9: CAN Core Bus Interface.        | . 30 |

| Figure 10: CAN Interface State Diagram   | . 31 |

| Figure 11: Hardware Reset                | . 33 |

| Figure 12: CAN Transceiver Schematic     | . 34 |

| Figure 13: CAN Transceiver Picture       | . 34 |

# **ACKNOWLEDGMENTS**

I would like to thank several people for their involvement in this project. I especially want to thank Dr. Russell Duren without whose help the Verilog portions of this project would have been overwhelming. I would also like to thank Dr. Steven Eisenbarth for his advice, assistance, and patience in the real-time programming aspects of this project. Finally, I would like to thank Dr. Ian Gravagne for the privilege of assisting him in this research.

# **DEDICATION**

# TO

Rev. Tom Gibbs and Rev. Pete Hatton for their sacrificial involvement in Reformed University Fellowship at Baylor University

TO

Mr. Carol Stubbs who taught me the value of solid, Biblical teaching

TO My Parents

whose marriage continues to be the best picture of Christ and the Church I have ever witnessed

#### CHAPTER ONE

#### Introduction

A recent grant to the Baylor Electrical and Computer Engineering department from the National Science Foundation (NSF) created the need for the innovation documented in this thesis. The proposed research explores the possibility of using dynamic equations on time scales to help increase the efficiency of distributed control networks [19]. This possibility would allow network busses more flexibility in message timing, thereby increasing total bus throughput. In the words of Baylor Engineering's NSF proposal, this research would explore

"how real-time distributed control systems can more effectively share available resources, predict certain types of control-related faults and instabilities, and permit designers to maximize the number of nodes that operate on the network."

As the utilization of electromechanical sensors and actuators increases, the ability to communicate with them in real time and in rising numbers will become increasingly important.

The Controller Area Network (CAN) protocol was selected as the means for testing new time scales theories. The CAN protocol was chosen for several reasons. CAN busses use real-time message transmission, which is important when studying the timing characteristics of time scales. CAN is fast enough for most control applications. This makes CAN a practical choice for controlling physical systems in various applications. CAN is also a very flexible protocol. It is easy to add and remove CAN nodes from a bus or alter the way a CAN node behaves without disrupting

communication on the entire bus. This ability to develop and test a few CAN nodes and then scale up to dozens is convenient.

In addition to these characteristics CAN is already a widely used standard for real-time, distributed controller networks. As such, support, components, and documentation are readily available at low cost. Although CAN is an established protocol, development continues on many CAN standards and devices. Communities supporting and actively contributing to the CAN protocol are helpful in the development process. Standards also exist for evaluating bus timing and utilization. These standards will be useful in evaluating time scales effects and as benchmarks for traditional systems.

The NSF proposal outlines a specific test bed and specific testing procedures for testing time scales theories. The proposal calls for a CAN bus of 40 nodes. Desktop computers will monitor the network in real-time and also inject controlled, experimental traffic to monitor the traffic's effects on the bus. The CAN controllers developed by the author for this thesis are that test bed. Primarily, this thesis describes and documents the development and implementation of the two types of CAN controllers that will be used for this experimentation. Development of the CAN controllers for real-time desktop computers that monitor the network are presented in Chapter Four. Development of the CAN controllers for the functional nodes of the CAN bus are presented in Chapter Five. Fundamentals of the two systems used for this implementation are discussed as they relate to the CAN controllers. Characteristics of the CAN protocol that make it a desirable medium for these experiments are described in the next chapter. These CAN controllers' ability to meet the time scales testing requirements and to be implemented on

two powerful platforms makes their development and implementation an ideal subject for this thesis.

## **CHAPTER TWO**

# General Description of CAN

CAN is the predominant real-time networking solution in a variety of industrial fields. CAN was initially developed in the 1980s by Robert Bosch GmbH for automotive applications [10]. Today CAN has been recognized worldwide as a standard, and it, or a derivative of it, is used in the majority of high-end European automobiles. CAN is also an important communication protocol in industrial applications, avionics, and safety critical applications.

One interesting characteristic of the Bosch CAN specification is its omission of a communication medium. This omission allows for a variety of CAN bus media. Any medium that clearly possesses dominant and recessive states can be utilized as a CAN bus. CAN busses have been implemented on differential voltage wire pairs, single wires with a ground, and even wireless transmitters [14]. The International Standards Organization (ISO) standardized a 5V differential electrical bus for up to 1Mbit per second CAN communication in ISO11898-2 [1]. This is the most common implementation of a CAN bus.

Controller Area Networks are made up of CAN nodes that interface with the bus. Figure 1 depicts four CAN nodes connected to a CAN bus. Each of these nodes is an independent CAN controller. Every node sees every message, or frame, that is transmitted on the bus and acknowledges the message if received correctly. Several

characteristics make CAN the most suitable test bed for real-time distributed control research.

Figure 1: CAN Nodes – Multiple CAN nodes with various functionality all connect to a single CAN bus to control and analyze a physical system.

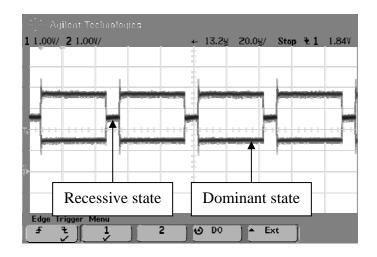

The first important characteristic of CAN that qualifies it as an appropriate medium for this research is the inherent prioritization in the network's architecture [1], [2]. Figure 2 shows the dominant and recessive states of a differential voltage CAN signal. CAN is a multi-master protocol, so any node may send a message at any time as long as the bus is free. Nodes determine whether or not the bus is free by monitoring the state of the bus at all times. If the node senses activity on the bus, it receives the incoming message. If a node senses a dominant state on the bus while it is transmitting a recessive state, it must immediately stop transmitting and process the incoming message with the higher priority. When two nodes contend for the bus, the message with the highest priority is always transmitted first. This is accomplished with a clever bitwise arbitration using the identifier of the CAN frame.

Since CAN is used in safety-critical applications, it is important that messages arrive within a specified amount of time. Guaranteed latency is also important for evaluating time scale theories because the nature of the experiments is sensitive to timing.

Figure 2: Differential CAN Signal – This differential CAN signal demonstrates the dominate and recessive bus states. The two wires float to 2.5V when the two bus wires are not being driven 2V apart. The top two bus wires are placed on top of one another to highlight the differential nature of the signal as it is seen on the "CAN HI" and "CAN LO" wires on the CAN bus.

The inherent prioritization of CAN frames ensures that critical messages will be sent ahead of less important messages. A critical message may be sent as long as the bus is not currently being accessed. If another node is transmitting, a critical message need only wait until the message currently on the bus has finished before gaining bus access.

The maximum latency of a critical message is only impacted by two factors. In the worst case scenario, a critical message needs to be sent just after a less critical message has been put on the bus. The critical message only needs to wait the length of one CAN message, since the critical message's priority ensures that it will be transmitted as soon as the current message has finished. The second factor that may delay a critical message from being sent is bit stuffing. If more than five consecutive bits of the same polarity occur in a message, the node must insert one bit of opposite polarity. This "stuffed" bit contains no information and is used solely to synchronize the timing between the transmitting node and receiving nodes. Once received, the stuffed bit is

discarded. These two factors and the interframe space of a few bit times combine to give the maximum latency for a critical message.

CAN is a message-based protocol as opposed to an address-based protocol [2]. The fact that every message contains all relevant priority and data information makes CAN an ideal way to study timing characteristics of a network. A CAN network is very flexible as well. Since all nodes receive, acknowledge, and decide whether or not to process a message, it is trivial to increase the number of nodes on a CAN bus. This is important for the test bed being developed since development and testing are easier with a small number of nodes, while experimentation requires a large number of nodes.

Another useful implication of a message-based network is the ability to "multicast" one message to many or all of the nodes at once. This is useful in bus reconfiguration and when it is necessary to communicate to multiple nodes.

Another defining attribute of CAN networks is their ability to address and recover from node faults and a variety of bus errors. The Bosch CAN specifications [2] outline several possible CAN errors and give actions to be taken when they are encountered. By detecting and addressing these errors it is difficult for the entire CAN bus to be brought down by one faulty node.

The CAN specification gives four methods for error checking. The first is monitoring at the transmitter. If the transmitting node is transmitting a dominant bit and monitors a recessive bit on the bus, an error has occurred. Likewise, a dominant bit on the bus while a recessive bit is being transmitted triggers an error state. Another error checking method is the Cyclic Redundancy Check (CRC). Every node computes a CRC for the message on the bus and then compares it to the CRC that has been computed by

the transmitter. If a node detects an error in the CRC, the frame is discarded by the receiving nodes and re-sent by the originating node [1]. The third method of detecting errors is the bit stuffing check. This simply generates an error if more than five consecutive bits of the same level occur. The final error check is for form errors. CAN frames have several locations that must have either a dominant or recessive bit. If a node monitors an out of place bit in one of these fields, it generates an error. These error checks and fault confinement procedures keep a CAN bus operable even in the face of a significant number of errors.

Error confinement is another important aspect of CAN error handling. When a single node encounters errors, it enters into an "error active" state. When in an error active state, a node may still participate in bus activities and acknowledge received messages until the number of errors exceeds a preset limit; then the node transitions into an "error passive" state. Nodes in an error passive state may not transmit acknowledge bits, but may continue participating in bus activities in a slightly more limited state. If errors continue to occur, the node's drivers are switched off. If a node receives enough messages correctly, it may move out of the current error state to a lower error state. This effectively contains errors in a faulty CAN node to that node instead of allowing it to bring down the entire bus.

The speed at which CAN frames can be transmitted makes it good for most control applications. Basic CAN frames have eight or fewer data bytes. These relatively short frames and comprehensive error checking allow CAN messages to be transmitted fast enough so that they are useful to most physical systems. The Bosch CAN specification does not give specifications for the speed at which CAN messages may be

transmitted. However, the ISO 11898-2 standardization for a dual-wire differential voltage CAN bus set the maximum speed to 1Mbit per second [13]. The maximum bus length for communication at this rate is in the tens of meters and is limited by the speed of the electrical signal as it propagates down the wire and back before the node is able to monitor the correct level on the bus [14].

CAN is a communication protocol whose popularity continues to grow. The characteristics of CAN busses allow them to be used for communication between many parts of real-time systems. The ability to use CAN for real-time systems qualifies it as an excellent medium for time scales testing provided that bus diagnostics, experimentation, and monitoring can be run in real time as well.

# CHAPTER THREE

# Technology Used in CAN Bus Implementation

The CAN bus developed for this project has two types of nodes. The first node is controlled by a PC running the QNX real-time operating system (RTOS). This type of node is responsible for monitoring network traffic, analyzing the traffic, and generating experimental traffic. The controller developed by the author for this node type is an Arcom board that uses Philips' SJA1000 CAN controller. The second type of CAN node performs small tasks such as reporting sensor values, actuating devices, or displaying data at remote locations. These nodes are made up of Nintendo Gameboy Advance (GBA) SPs and a device named the Xport 2.0 from Charmed Labs, both of which will be discussed later.

## *QNX Real-Time Operating System*

QNX is a real-time operating system, meaning that a thread's utilization of the processor is determined by the thread's priority and the priorities of the other threads competing for processor time. The thread with the highest priority always has access to the processor. In practice this means that critical inputs are addressed immediately and the corresponding critical applications are assured processor time as soon as it is needed instead of having to wait for processor resources [15]. QNX has been designed to run a variety of real-time applications from embedded applications with stringent memory requirements to symmetrical multi-processor machines that perform high speed, critical calculations. The emphasis QNX Software Systems Limited (QSSL) places on

development makes QNX an ideal platform for developing a real-time CAN bus analyzer. Several aspects of the QNX operating system are important in driver development.

#### Scalable Architecture

QNX's nucleus is its microkernel. QNX allows a user to add or remove various modules that would automatically be included in a traditional kernel [3]. This scalable architecture is what allows QNX to be so flexible. These components can be process managers, a file system, drivers, and applications. Components can be added and removed in real time at the user level. In order for different components to communicate, QNX uses a technique called message passing. Apart from direct kernel calls, which generally deal with thread scheduling, all modules interact with messages. Messages are passed between "servers" and "clients" in QNX. Clients request information from a server by sending a message to the server. Once the request has been sent, the client blocks, or waits, until it receives a message back from the server with the information it needs. In this message paradigm it is important for the clients to initiate messages to the servers because having a server that was blocking on a reply from a client would slow the system and compromise real-time execution. Most messages are sent and received without having to write specific message-sending code. The QNX POSIX libraries are already populated with functions that handle most message sending tasks; although, when writing a resource manager with POSIX functions, message passing is important.

# Resource Managers

A resource manager can be described as a set of functions that allow a user access to some service or device [3]. A QNX resource manager is commonly known as a driver on other systems. When a user needs to access a device, the resource manager provides specific functions that allow the user to interact with the device at a higher level. For instance a serial port and modem will not use the same techniques for reading incoming data; however, a user can read from both devices using the *read()* command once the device has been opened. The resource manager for the modem provides a different functionality for the *read()* command than the serial port's resource manager, but the user can access them, and a host of other devices and services, with the *read()* function.

All operating systems have some form of resource manager or library for abstracting device operations. QNX is unique because its resource managers run at thread-level. QNX does not treat a resource manager any differently than it would treat a program displaying the time to the screen. Since a resource manager is not directly associated with the kernel or any other module of the operating system, it is not difficult for a user to start and stop the resource manager when needed. The ability to start and stop resource managers on the fly makes the development of resource managers much simpler than it would be otherwise.

# Interrupts

Most devices operate with some type of interrupt. Interrupts allow devices to react to an external input or a condition by gaining processor access immediately at the occurrence of the event. Interrupts are obviously important to real-time systems, since real-time systems typically need to react to a host of inputs. While interrupts allow a

system to react to stimuli in a timely manner, they come with the overhead of a context switch every time there is an interrupt. QNX's microkernel architecture give it very fast context switches. On an x86 processor QNX can switch contexts in 21 instruction cycles [16]. This low cost for context switching allows QNX to handle multiple threads smoothly while continuing to respond efficiently to interrupts generated by various real-time dependent peripherals.

QNX has two methods of handling interrupts. *InterruptAttachEvent()* is typically used for devices that do not interrupt frequently and that do not require immediate attention when they interrupt. *InterruptAttachEvent()* attaches a continually running thread to an interrupt. This thread blocks on a message telling the thread that there has been an interrupt that needs to be serviced. When an interrupt occurs, the kernel masks the interrupt and sends a message to the thread to handle the interrupt. Once the thread has cleared the interrupt source, the thread unmasks the interrupt, loops, and blocks on an interrupt message from the kernel again. This method of handling interrupts requires no interrupt service routine (ISR). The entire handler runs at thread, or user, level. This lessens the possibility of crashing the system if an interrupt hangs or the device malfunctions. One drawback to *InterruptAttachEvent()* is that it unblocks on every interrupt regardless of a given interrupt's relevance to the interrupts that are being checked by the interrupt handler thread.

The second method of interrupt handling in QNX is *InterruptAttach()*. *InterruptAttach()* runs an ISR for a particular interrupt and then decides whether or not to schedule a thread to run at user level. The ISR is responsible for clearing, or at least masking, the interrupt. If the device does not need urgent attention, the ISR can simply

schedule a thread to perform the task later and exit. If the device does need attention immediately, it is given the highest system priority as an ISR. The drawback to <code>InterruptAttach()</code> is that there is always some context switching involved. If frequent, unnecessary interrupts occur the system's performance may be slowed. Between these two interrupt handling methods QNX is able to respond to a variety of real-time stimuli.

## Arcom AIM104-CAN Controller Board

In order to utilize the benefits of QNX, a resource manager for a CAN controller had to be written by the author. The CAN controller selected was an Arcom board originally designed for PC-104 systems [4]. Once fitted on an adapter card, this board was able to interface with the system hardware through the ISA bus. All CAN aspects of the Arcom card are handled by a Philips SJA1000 CAN controller. The developer communicates with the SJA1000 by writing to and reading from its registers. The address space of the SJA1000 is mapped to some base address in the QNX's address space. The base address is set using jumpers for the upper 8 bits of the address. The interrupt request (IRQ) line is also set using jumpers on the Arcom board. The Arcom board provides an additional register for lighting three tri-color LEDs as well as EEPROM memory that stores information about the AIM104-CAN card. (The latest documentation for the AIM104-CAN is one revision earlier than the version of the PCB used in this project. The AIM104-CAN PCB used in this system is Version 2, Issue 1. The latest documentation for the AIM104-CAN is Version 1, Issue 2. This did not pose significant problems; however, the document section "Isolated CAN Transceiver" that states the CAN transceiver requires "external powering in order to function" is no longer

correct, as the transceiver is powered from the ISA card. There are still connections for external powering, so care should be taken when attempting to boost transceiver power.)

# Nintendo Gameboy Advance SP

When Nintendo developed the Gameboy Advance (GBA) it was immediately recognized as a novel, yet powerful, development target. Before the GBA was even sold, PC emulators were already being developed to test gaming applications. The GBA has two microprocessors onboard [17]. In order to support legacy games from the original Gameboy, the Nintendo engineers included the old Z80 processor on one side of the PCB. In order to run newer, more processor- and graphics-intensive games, the other side of the PCB is fitted with an ARM7TDMI 32-bit 16.78 MHz RISC processor. This processor is commonly used in a variety of technologies from cell phones to Ethernet routers. Old games used a 16 bit bus to transfer information from the game cartridge to the Z80 processor. However, new games use a 32-bit bus. In order to support legacy game cartridges, the new GBA must multiplex address and data information across the old 16-bit bus. Once the intricacies of the GBA are mastered, the GBA is a powerful embedded system. The GBA possesses a 240 x 160 pixel TFT color display, a communications port capable of several modes of operation, ten user input buttons, four channel analog sound output, and internal power supply [17]. All of these features are well documented and supported by freeware libraries, including the GNU code development tool chain.

# CharmedLabs Xport 2.0 and XRC

The Xport 2.0 is a flexible and elegant solution to the problem of harnessing the power of the GBA without intensive hardware development. In the words of the Xport

developers, CharmedLabs, the Xport "turns the Game Boy Advance into a powerful embedded development system." The Xport combines the flexibility of a Field Programmable Gate Array (FPGA) with the processing muscle and convenient I/O of the GBA. The reconfigurable FPGA allows a developer to integrate almost any hardware functionality into the Xport. The Xport also contains flash memory that the GBA boots from and 64 I/O pins that are programmable through the FPGA. CharmedLabs provides a thorough, although completely undocumented, library of functions to control many of the GBA features and all of the Xport's functionality.

# Xilinx Spartan II FPGA

The ingenuity and flexibility of the Xport lies with the FPGA. Xports are manufactured with two types of FPGAs. The version used for this project was a Xilinx Spartan II XC2S150. This FPGA has a 50 MHz clock and 150,000 gates. The XC2S150 comes with 260 I/O pins; although, only 64 are provided to the user through the Xport. CharmedLabs uses the FPGA to demultiplex the GBA's multiplexed data and address bus. Direct communication with the GBA is abstracted so developers using the Xport have clearly defined components with which to work. The speed, number of gates, and outputs of this FPGA made the Xport an ideal target for a CAN controller implemented in the FPGA's hardware.

## *Xport Robot Controller*

An optional accessory to the Xport is the Xport Robot Controller (XRC), also developed by CharmedLabs [6]. The XRC, while not critical to development of a CAN controller, provides functionality for the CAN nodes. The XRC provides several data

collection options and several actuator options. These features include four motor controllers, digital I/O, analog sensors, a Bluetooth module, and infrared proximity sensors. CharmedLabs provides Verilog libraries for implementing the XRC functionality in the FPGA and software libraries, including a patent-pending method of closed loop feedback for DC motor control. These peripheral devices, while not directly related to the implementation of a CAN node, provide the functionality that a CAN node will need to be useful in a physical system.

# CharmedLabs Open-Source Libraries

CharmedLabs provides the libraries necessary for a user to work with the Xport and XRC as source libraries. These libraries fall into two broad sections: Verilog source code for the FPGA and C++ libraries for the GBA. The Verilog library's most important component is the *Primary()* module. This module is responsible for decoding the GBA bus and streamlining communication from the flash to the GBA. This primary module has to be instantiated as the top module of every project so that it can access the FPGA pins that are routed to the GBA's cartridge slot. Once the bus has been decoded, developers have access to a 24 bit address bus, a 16 bit data write bus, a 16 bit data read bus, a vector of interrupts, a vector of lines to clear interrupts, a clock signal, and a reset signal. The XRC peripherals are also included as Verilog source modules. These modules can be instantiated in the same module as *Primary()* and handle the hardware needs of the motor controllers, general purpose I/O, optical encoders, and the Bluetooth module.

The second group of libraries is the C++ source code that controls the various aspects of the Xport's operation. Each peripheral has a C++ class that contains its control

methods. For instance, the infrared sensors have a class with functions like SetXirPower(), GetXir(), and SetXirRingLength(). One of the most useful classes is the interrupt controller class. When the interrupt controller is instantiated, all interrupts are directed to its ISR. When a user needs to use an interrupt, the user creates a class method named Interrupt() and registers it with the interrupts controller along with an interrupt number. If the interrupt is an external interrupt, the interrupt number corresponds to the interrupt's location in the Primary() module's interrupt vector. Once the interrupt is registered, whenever that IRQ line is raised, the interrupt is masked and the class's Interrupt() method runs to clear the interrupt. CharmedLabs also provides utility classes such as a text display class and a class for creating menus. These libraries allow the Xport and XRC's functionality to be exploited smoothly and quickly.

# OpenCores.org CAN Core

The CAN functionality of the Xport comes from a CAN controller implemented in the FPGA. OpenCores.org is a website that provides open source hardware cores. A hardware core is a hardware configuration that can be implemented on an FPGA. Cores typically come in source code versions or pre-compiled into a library. OpenCores.org has only one CAN core [7]. This core was developed by Igor Mohor and is shared as source code on OpenCores.org. This core is loosely based on the SJA1000; although, this core uses active high CS, RD, and WR signals instead of active low signals like the SJA1000. The OpenCores.org CAN core is controlled by writing to and reading from addresses that can be memory mapped. This CAN core also uses an 8051 style bus. An 8051 bus shares a single 8 bit bus for address and data. The bus function is controlled using ALE, RD, and WR signals. The CAN core has interrupts that function like the

SJA1000 as well. One drawback to this open source core is the lack of documentation.

A brief functional diagram is provided on the OpenCores.org website, and the testbench gives some indication of the interface and functionality.

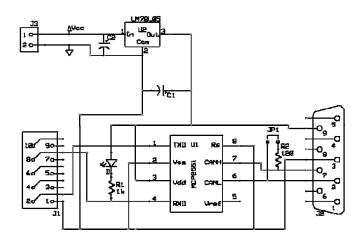

# Microchip MCP2551 CAN Transceiver

The final piece of hardware used to outfit the Xport for CAN bus interaction is the CAN transceiver. The transceiver used is a MCP2551 from Microchip. This is a simple IC that converts the 5V differential signals from the CAN bus to a TTL receive signal for the FPGA (Figure 3). Conversely, the transceiver converts TTL output from the CAN core to a signal that operates on the CAN bus. This 8 pin IC is the last link in this developmental CAN bus.

Figure 3: TTL to Differential CAN – The MCP2551 translates standard TTL levels to a 2.5V differential CAN signal. "CAN\_TX" is the data input to the MCP2552.

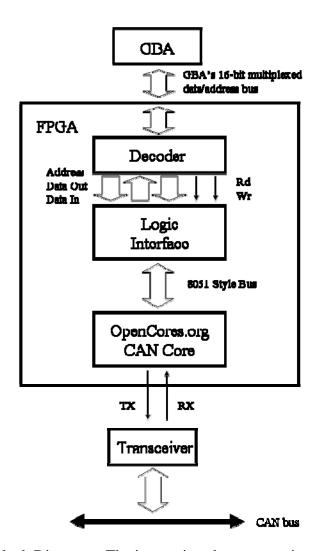

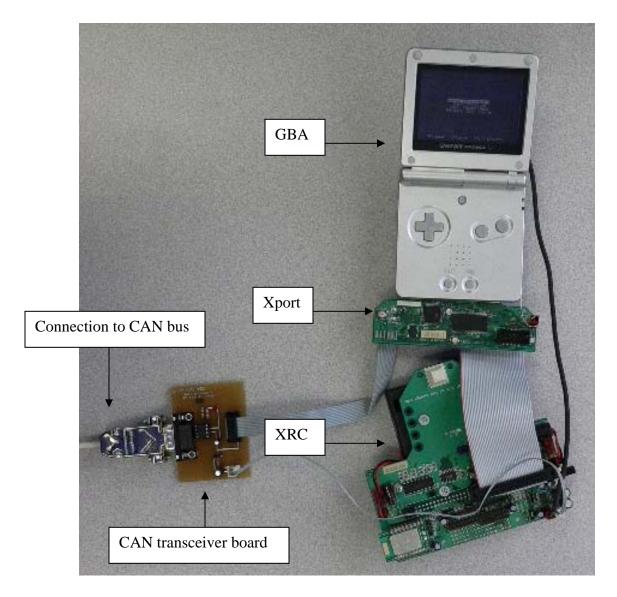

The final configuration of these components allows the GBA-Xport combination to function as the processor and hardware for the CAN controller while the MCP2551 connects the transmit and receive lines of the OpenCores.org CAN core to the CAN bus. A block diagram of the final configuration can be seen in Figure 4, and a photograph of a complete GBA CAN node developed for the thesis is given in Figure 5.

Figure 4: GBA-Xport Block Diagram – The interactions between various levels of the GBA and Xport's interface to the CAN bus are illustrated in the figure above.

Figure 5: CAN Node Picture – Final configuration of the GBA, Xport, XRC, and CAN transceiver.

## CHAPTER FOUR

# **QNX** Driver Development

Use of the AIM104-CAN board with the QNX operating system required a resource manager to be developed. Since QNX is similar in many ways to Linux, the decision was made to develop a resource manager by modifying an existing Linux driver that supported an ISA bus interface to Philip's SJA1000. Can4linux is an open source CAN driver that supports the SJA1000. Once can4linux had been completely rewritten for QNX, the project was renamed can4qnx. The major components developed by the author are described in the following chapter. Individual functions and files written for this thesis are documented, described, and included in their entirety in Appendix A.

## SJA1000 Access Functions

The lowest level driver functions access the SJA1000 directly. These functions are responsible for the direct communication with the SJA1000's registers. By packaging the register operations used to communicate with the SJA1000 into a form that is easier to deal with, operations requiring several steps can be simplified to one function call. These functions deal with everything from initializing registers of the chip to setting up timing to handling interrupts. All the devide communication is done using QNX's *in8()* and *out8()* commands; although, these commands themselves are hidden by macros. In order to access registers in an intuitive manner a data type named *canregs* is defined. *Canregs* is a structure of 8-bit elements with names corresponding to the registers of the SJA1000. By typecasting the base address of the device as a pointer to a *canregs*

structure, the SJA1000's registers can be referred to by the member names in *canregs*. Bit values are defined for each register so that their purpose is more easily inferred. QNX's *usleep()* function is used to slow down I/O when a delay is necessary during device communication.

# Interrupt Handler

One of the keys to receiving and transmitting CAN messages efficiently and quickly is the use of interrupts. Can4qnx uses the *InterruptAttachEvent()* method of interrupt handling. *InterruptAttachEvent()* works well for a SJA1000 based CAN controller because the interrupts that are generated do not occur frequently enough to derail real-time operation. The SJA1000 can be configured to generate interrupts on various events or not at all. In BasicCAN mode, the mode used in this project, the SJA1000 generates interrupt on wake-ups, receive FIFO overruns, errors, transmits, and receives. The relative frequency of these is low when compared to the processing speed the QNX system, so *InterruptAttachEvent()* works well.

The interrupt handler thread is simply a function written by the author called  $CAN\_Interrupt()$  that is started from the resource manager. Since InterruptAttachEvent() is being used, the handler is just another thread that unblocks when an interrupt is generated. When  $CAN\_Interrupt()$  runs, the thread registers itself with the kernel and then blocks on an interrupt. Once an interrupt is received,  $CAN\_Interrupt()$  unblocks and checks the SJA1000's status register to determine what generated the interrupt. Reading the status register also clears the interrupt. If the status register does not show that there are any interrupts needing to be cleared,  $CAN\_Interrupt()$  loops and blocks on the next interrupt. If the SJA1000 has generated the interrupt, it is addressed. In the case that a

received CAN message generated the interrupt, *CAN\_Interrupt()* reads the appropriate registers using the SJA1000 access functions described above and stores the message in a receive queue. If a CAN message transmit generated the interrupt, *CAN\_Interrupt()* checks to see if there are any messages in the transmit queue and sends the next one if there are. If the interrupt was generated by an error, *CAN\_Interrupt()* increments error counters. In the case of an overrun, the overrun counter is incremented and the overrun status is cleared. After the interrupt has been cleared, *CAN\_Interrupt()* unmasks the interrupt so subsequent interrupts will be received.

## I/O and Connect Functions

The QNX connect functions and the QNX I/O functions are the functions used when the device receives standard POSIX function calls like *read()*, *open()*, or *devclt()*. The prototypes for these functions are specified to reflect the parameters and return values that are expected by QNX. For example, *open()* is a connect function that returns a non-zero *int* value if the file is opened successfully. The *open()* function is passed a pointer to an open context block (OCB), an open message, and two pointers to shared address space. The *open()* function stores the context in the data space of the OCB. Once *open()* has been called by a program, that program has a file pointer, and I/O functions can be called. The I/O functions are passed messages from the client, the OCB initialized by *open()*, and a low-level context block. Inside the connect and I/O functions written for this resource manager the SJA1000 access functions are used to execute the commands or obtain the data that the program requires. When a program calls the *read()* function, the *read()* function checks for any new CAN messages. If there are no new messages, the *read()* function returns a zero. If there are new messages, the *read()*

message returns a pointer and the number of bytes requested by the program in a canmsg\_t structure. Details of other I/O and connect functions written for this project can be found in Appendix A.

# can4qnx Resource Manager

In QNX, the resource manager is the interface between the user and the device.

The heart of a resource manager is an infinite loop that blocks on a message from a client.

Once a message is received the resource manager responds to the message using various device specific connect and I/O functions.

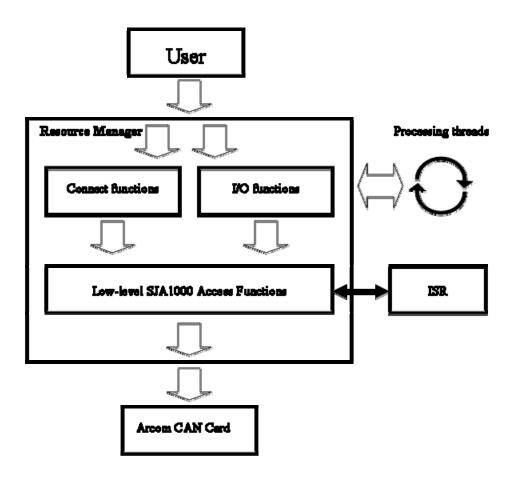

The top level interface for a resource manager looks very similar for any device. In this CAN controller resource manager's main() function several configuration variables are initialized to default values. The CAN controller's make and model are set; the default baud rate is set to 125kbits per second; the acceptance code and mask's default values are set to accept all incoming message identifiers; and the value for the output control register is assigned. The resource manager must know the connect and I/O function addresses. QNX provides a default set of connect and I/O functions so that a message for a unsupported operation does not crash or hang the device. Once the connect and I/O functions have been given default values, the device specific connect and I/O functions are assigned, overwriting the default functions. These functions are now used when a user requests a POSIX function related to this device. Next, a mechanism for dispatching threads to handle device requests is implemented. Finally, the thread for handling interrupts is created, and the low-level context of the device is stored. Once these tasks are completed, the resource manager simply waits for client messages (Figure 6).

The implementation of the abstracted levels described above allows a user to interact with the Arcom AIM104-CAN in a normal, POSIX compliant manner. When a user program accesses the device in the prescribed manner, the QNX real-time system becomes a powerful CAN node.

Figure 6: Resource Manager Block Diagram – This is a block diagram of the resource manager and its interaction with the user, processing threads, ISR, and Arcom CAN card.

## **CHAPTER FIVE**

# **Xport CAN Controller Development**

Several interfaces needed to be considered and developed for this thesis in order to assemble the various pieces of the CAN controller for the Xport. The GBA has a method of handling interrupts that is different than the CAN controller's method for generating and clearing interrupts. The GBA also uses a bus structure that does not fit simply into the CAN controller's architecture. These interfaces proved to be the most difficult aspects of this project.

#### Bus Description and Behavior

The most important aspect of the GBA-CAN core interaction is interfacing the GBA's address and two data buses to the CAN core's bus. The SJA1000, and hence the OpenCores.org CAN core, use an 8051 style bus. This bus format shares a single 8 bit bus for both address and data transmission. Addresses are transmitted first, followed by data. Three control signals are used: Address Latch Enable (ALE), Read (RD), and Write (WR). The address is latched into the CAN core on the falling edge of ALE. Once the address has been latched, data is driven by either the GBA or CAN core depending on whether the RD or WR strobe is raised. The GBA raises RD for the CAN core to drive data onto the bus and raises WR when the GBA is writing data to the CAN core.

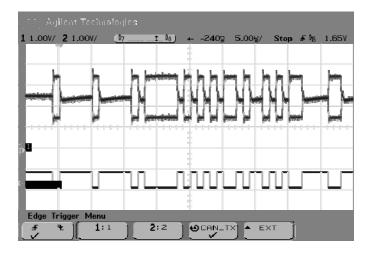

The Xport presents three busses that the GBA uses to communicate: a 24 bit address bus, a 16 bit data write bus, and a 16 bit data read bus. The GBA also uses *Rd* and *Wr* lines. When the GBA reads or writes, the address becomes stable about 300ns

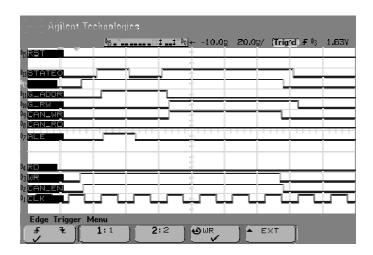

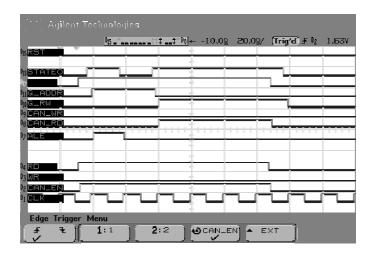

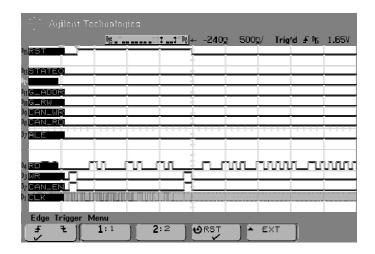

before the Rd or Wr line is raised. Once the address is stable, the Wr line is raised and the data write bus is latched on the falling edge of Wr [18]. When the Rd line is raised, data is driven onto the data read bus for the duration of the signal. Behavior of a write and read to the CAN controller's address space can be seen in Figures 7 and 8, respectively.

Figure 7: Write to CAN Address – This figure is an oscilloscope capture of a write to the CAN controller's address space. State changes can be seen by looking at "STATEO", the least significant bit of the current state. The state machine begins in the idle state and returns to the idle state once "WR", the GBA's *Wr* strobe goes low. "G\_ADDR" is the *gateaddr* signal. "G\_RW" is the *gaterw* signal.

Figure 8: Read from CAN Address – This figure shows a read to the CAN controller's address space.

#### GBA to OpenCores.org CAN Controller Bus Interface

A minimalist approach was used by the author to streamline the state machine and the registers used by the state machine to control the CAN core (Appendix C).

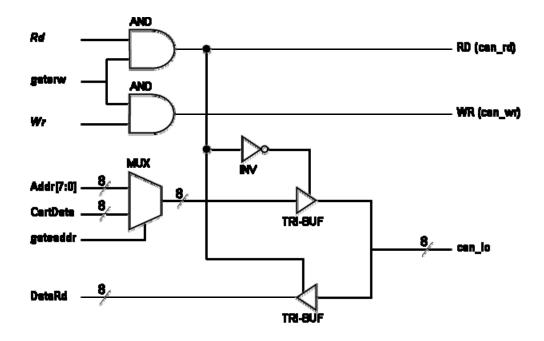

Combinational logic and two control registers, *gateaddr* and *gaterw*, allow for a simple interface between the two bus structures (Figure 9). An enable signal brings the state machine in and out of its idle state. This enable signal is assigned a high using combinational logic as soon as the address is in range and a *Rd* or *Wr* strobe is raised.

The RD and WR signals to the CAN core are gated straight from the GBA's *Rd* and *Wr* signals with the *gaterw* register whose value is assigned in the state machine. The 8 bits of the data read bus are always high-z unless the RD signal is high, in which case it is assigned the 8 bits of the CAN core's bus. The CAN core's bus is slightly more complicated. If the RD signal is low and *gateaddr* is high, the CAN core's bus is assigned the lower 8 address bits. When RD and *gateaddr* are low, the CAN core's bus is assigned the GBA's bus of data to be written. The CAN core's bus is assigned high-z values if RD is high, so that it can monitor the bus for the data being written by the GBA.

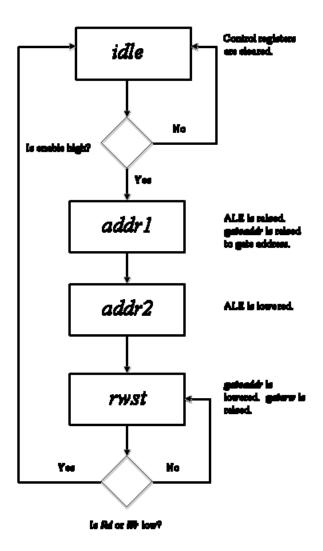

Since the CAN core's bus has specific timing characteristics, a state machine was implemented to interface the busses (Figure 10). Four states are used. The first state is the *idle* state. This is the initial state after a reset. During periods when there is no activity between the CAN core and GBA, the interface is in the *idle* state. All control registers are cleared in this state. The *idle* state always returns to *idle* unless the enable signal goes high indicating that the address has stabilized in the CAN controller's range. Once the address is in range, the state machine moves to the first address state, *addr1*. In *addr1* the ALE line is raised for a clock period and the lower eight bits of the address bus

Figure 9: CAN Core Bus Interface – This is a schematic of the combinational logic that gates address and data over the 8051 style bus to the CAN core. "BUFE8" is a tri-state buffer that controls the direction of data flow on the bus. "M2\_1" is a multiplexer controlled by *gateaddr* that chooses whether to send address or data to the CAN core.

proceeds to *addr2*. In *addr2* the ALE line is lowered to create a negative edge.

Lowering ALE latches the address, and the state machine moves to the *rwst*. In *rwst gateaddr* is lowered, *gaterw* is raised, and depending on whether the GBA has the *Rd* or *Wr* line raised, data is driven onto the CAN core's bus from the GBA's bus, or the GBA's

bus is set to high-z so that data can be read from the CAN core. The state machine

remains in *rwst* until the *Rd* or *Wr* signal goes low. The state machine returns to the *idle*state once the enable signal goes low.

The entirety of this state machine runs during the time when Rd or Wr is high. Since the FPGA is running at 50 MHz and the GBA's processor is only running at 16.78 MHz timing is not a problem. By waiting until one of the Rd or Wr strobes is raised, the address is guaranteed to be stable and the data is guaranteed to be ready. Having the

CAN core run almost three times as fast as the GBA also assures plenty of time for the CAN core to drive its data onto the bus during a read.

Figure 10: CAN Interface State Diagram – This is a diagram of the state machine used by the logic interface. States are shown in rectangles, and decisions are shown as diamonds.

## CAN Core-GBA Interrupt Interface

Interrupts are an important part of the GBA-CAN core interface. The CAN core uses active low interrupts. These interrupts are cleared when the interrupt register of the CAN core is read. The Xport interface with the GBA expects active high interrupts that

are cleared when a corresponding IRQ clear line is raised. To reconcile these two interrupt techniques a hardware interrupt mask was developed for this project. When the CAN core generates an interrupt, it is inverted to active high, and ANDed with the interrupt mask before being sent to the GBA. The interrupt mask is set synchronously by reading the reset signal, IRQ clear line, and interrupt line from the CAN core. After a reset the interrupt mask is set to high unmasking the interrupt. If the IRQ clear line is raised, the interrupt mask is set to low. This masks the interrupt from the GBA. If the interrupt line from the CAN core goes low, indicating that the interrupt has been cleared by a read of the status register, the interrupt mask is raised on the next clock cycle. It is up to the software developer to unmask the interrupts by reading the status register, or to clear the interrupt before the IRQ clear line is raised by reading the status register if the corresponding CAN controller software discussed below is not being used.

#### Hardware Reset Register

The ability to reset the CAN core's hardware through software was added to the CAN core interface for this project. To the software developer this simply looks like another register following the existing CAN core registers. This register stores the last bit of the data bus into a one-bit reset register on the negative edge of *Wr* when the address bus points to this register. This register is tied to the reset line of the CAN core. This is useful because it allows a program to return the CAN core to a known state with the reset signal on the CAN core. Figure 11 shows a write to raise the reset line of the CAN core and another write to lower the reset line.

Figure 11: Hardware Reset – This figure shows writes to the reset register of the CAN interface logic. As seen in the "RST" signal, these writes raise and lower the reset line on the CAN controller.

## CAN Transceiver

A custom PCB was created for the MCP2551 to connect to the Xport's  $can\_wr$  and  $can\_rd$  and the CAN bus. This CAN transceiver board connects to the CAN bus using a standard DB-9 connector. This board can be terminated with a  $120\Omega$  resistor by adding a jumper. It also has an LED that lights when the bus is active and is powered from an auxiliary power output on the Xport. A schematic (Figure 12) and photograph (Figure 13) of the board can be found below.

#### CAN Core Library Class

To manage the OpenCores.org CAN core and the functionality of the interface logic, a controller class was written by the author. This class, *CCanCore*, is responsible for everything from low-level register manipulations, to handling interrupts, to high-level user interaction. The *CCanCore* class is written in a similar fashion to any other Xport peripheral class. The interrupt mask implemented in the CAN interface module allows

the *CCanCore* class to use the interrupt handling provided in the CharmedLabs libraries.

The ISR in the CAN controller class automatically clears and unmasks the interrupt when it occurs. This class is described in detail in Appendix B.

Figure 12: CAN Transceiver Schematic – This is a diagram of the custom CAN transceiver. J3 is the power connector. J2 is the DB-9 connector to the CAN bus. J1 connects to the I/O pins of the Xport's FPGA.

Figure 13: CAN Transceiver Picture – This is a photograph of the final CAN transceiver board.

#### Conclusion

Pairing the OpenCores.org CAN controller on the Xport and the Arcom AIM104-CAN board on the QNX RTOS gives a powerful real-time communication backbone for a control system. Both systems present an intuitive, well documented interface that will allow for their fast and efficient utilization. QNX's lean real-time operation paired with a CAN interface card allows it to be used as an effective node on any CAN bus, and the flexibility of the Xport combined with the convenience of the GBA's embedded system supplements the usefulness of the CAN controller implemented in the Xport's hardware. The system developed for this thesis will easily support further research in time scales and other control applications.

**APPENDICES**

#### APPENDIX A

## Appendix Documenting Can4qnx Code

#### *ONX SJA1000 Access Functions*

CAN\_GetStat() is responsible for retrieving status information from the CAN

##

controller. The *CanStatuPar\_t* is a data structure defined in "can4qnx.h".

\_\_LDDK\_DEVCTL\_PARAM is defined in "can\_defs.h" and is the list of parameters for the resource manager's *can\_devctl()* I/O function. The value of the status register is

printed to stderr as a decimal int. This function always returns an int value of zero after

filling the data structure pointer to by *stat*.

#### int CAN\_ChipReset(), "can\_sja1000funcs.c"

CAN\_ChipReset() is responsible for returning the SJA1000 to reset mode and initializing the configuration registers to values defined elsewhere. If the board is not in reset mode after ten microseconds, this function returns a "-1". Otherwise, it initializes the clock register, mode register, interrupt enable register, and output control register. Finally, it calls the CAN\_SetTiming() function and CAN\_SetMask() function, passing them their respective default values. On completion a zero is returned.

#### int CAN\_SetTiming(int baud), "can\_sja1000funcs.c"

*CAN\_SetTiming()* configures the two timing registers on the SJA1000. The function switches on *baud*. If *baud* matches a baud that has been defined in

"can\_sja1000.h", the appropriate index is set for the *CanTiming* array that is initialized as a global in "can\_sja1000funcs.c". The indexed values are then written to the SJA1000. If *baud* does not match a predefined value, it is treated as a two 8 bit register values. The upper 8 bits are written to the first timing register, and the lower 8 bits are written to the second timing register. In this case the two register values being used are output to stderr. This function returns zero upon completion.

#### int CAN\_StartChip(), "can\_sja1000funcs.c"

*CAN\_StartChip()* is responsible for moving the SJA1000 from reset mode to normal operation. The *RxErr* and *TxErr* are reset; the receive buffer is released; the overrun status, if any, is cleared; and any interrupt is cleared. Finally, the interrupt enable register is initialized. Once these tasks have been completed, the mode register's reset request bit is cleared and the function returns a zero.

## int CAN\_StopChip(), "can\_sja1000funcs.c"

*CAN\_StopChip()* simply sets the reset request bit in the mode register and returns zero.

#### int CAN SetOMode (int arg), "can sja1000funcs.c"

*CAN\_SetOMode()* writes *arg* to the output control register and returns zero. This function must be used while the SJA1000 is in reset mode.

#### int CAN\_SetMask(unsigned int code, unsigned int mask), "can\_sja1000funcs.c"

CAN\_SetMask() sets the acceptance code and acceptance mask. code and mask

are treated as four 8 bit values. The most significant byte of code and mask corresponds

to the most significant 8 bits of the identifier. *CAN\_SetMask()* is for use when the SJA1000 is in PeliCAN mode and only then when it is in reset mode. This function always returns zero.

## int CAN\_SendMessage(canmst\_t \*tx), "can\_sja1000funcs.c"

CAN\_SendMessage() sends the CAN message pointed to by tx. All of CAN\_SendMessage()'s execution takes place with interrupts disabled. If CAN\_SendMessage() determines that the SJA1000's transmit buffer is busy, the message is enqueued in the transmit queue and a zero is returned. If the transmit buffer is free, the appropriate registers are filled with information from tx and the transmit request bit is set in the command register. After this, interrupts are disabled and the number of data bytes sent is returned. The return values are somewhat misleading, since zero could refer to either the number of data bytes sent or a busy transmit. A better method would be to return a "-1" or the number of items in the transmit queue as a negative number when the transmit buffer is busy.

#### int CAN\_GetMessage(canmsg\_t \*rx), "can\_sja1000funcs.c"

$CAN\_GetMessage()$  is responsible for retrieving a message from the receive buffer on the SJA1000 and filling the appropriate fields of rx.  $CAN\_GetMessage()$  first checks the overrun status and clears the overrun status if there has been a buffer overrun. If an overrun has occurred, a message is printed to stderr. If there is a message in the receive buffer, rx is filled with the relevant information. Once rx has been filled, rx is enqueued in the receive queue. If the receive queue is full, a message is printed to stderr.

*CAN\_GetMessage()* returns the number of data bytes received or zero if there was no new message. Once again, a better system of return values would be more useful.

#### int CAN\_VendorInit(), "can\_sja1000funcs.c"

CAN\_VendorInit() is responsible for memory mapping the device memory used by the Arcom AIM104-CAN to device I/O and for calling ThreadCtl() to give the current thread privity to map memory to device I/O. CAN\_VendorInit() uses several global variables declared in "can\_sysctl.c". can\_dev is of type uintptr\_t and points to the base address of the CAN board. Length is declared of type int, but is cast to a size\_t. Base is also declared as an int but cast to a uint64\_t. CAN\_VendorInit() uses the QNX function mmap\_device\_io() to map the memory. If mapping fails, a "-1" is returned; otherwise, a zero is returned.

## void CAN\_LoopLEDs(), "can\_sja1000funcs.c"

*CAN\_LoopLEDs()* chases the tricolor LEDs on the AIM104-CAN breakout board. LEDs chase for ten cycles.

#### Interrupt Handler

#### void \*CAN Interrupt(void \*data), "can sja1000funcs.c"

CAN\_Interrupt() is the interrupt handler thread for the AIM104-CAN board.

CAN\_Interrupt() creates an event structure which can be used for messages, pulses, or to start a thread [3]. ThreadCtl() is called to give this thread permission to attach an interrupt. The final initialization task is attaching the interrupt using

InterruptAttachEvent(). InterruptAttachEvent() attaches the event structure to interrupt IRQ which is defined in "can\_sysctl.c". InterruptID is assigned the return value from

InterruptAttachEvent(). On success IRQ\_requested is assigned a value of one. On failure, InterruptID is set to "-1" and IRQ\_requested is set to 0, which is the value it was initialized to, and the function returns a NULL value.

Once initialized, *CAN\_Interrupt()* blocks in an infinite loop until an interrupt occurs. When an interrupt is generated, the interrupt register is read, and if the CAN board did not generate the interrupt *CAN\_Interrupt()* loops and blocks on an interrupt again. If the interrupt was generated by the CAN board, each interrupt is checked and acted upon. If a receive interrupt was generated, the message is recovered and enqueued in the receive queue in a manner similar to *CAN\_GetMessage()*. If a transmit interrupt generated the interrupt, *CAN\_Interrupt()* checks for a message in the transmit queue and sends the next message if a message is waiting. If an error interrupt is generated, an error message is placed in the receive queue. If an overrun interrupt is generated, the overrun status is cleared and an overrun frame is placed in the receive queue. Finally, the interrupt is unmasked and the function loops to the top and blocks on another interrupt.

#### I/O and Connect Functions

#### \_\_LDDK\_OPEN\_TYPE can\_open(\_\_LDDK\_OPEN\_PARAM), "can\_open.c"

can\_open() is the connect function that a software developer calls to use the AIM104-CAN board. can\_open() checks to see if the device is already open. If the device is being used by another thread, an error is returned. can\_open() calls CAN\_VendorInit() to set up I/O communication with the CAN controller. If CAN\_VendorInit() returns an error value, can\_open() exits with an error. can\_open() proceeds to initialize the receive and transmit queues. CAN\_ChipReset() is called to initialize the CAN controller components. If CAN\_ChipReset() returns an error,

can\_open() exits with an error. CAN\_StartChip() is called to begin CAN bus activities using the AIM104-CAN board. A message indicating that the can\_open() function has been entered is printed to stderr. Finally, iofunc\_default\_open() is called with the original parameters and returned to the calling function to ensure that all of the correct QNX operations have taken place.

#### \_\_LDDK\_CLOSE\_TYPE can\_close(\_\_LDDK\_CLOSE\_PARAM), "can\_close.c"

can\_close() is the function that is responsible for closing communication between the AIM104-CAN controller and the thread calling the close() function. The first operation can\_close() performs is printing a message to stderr to announce that can\_close() has been called. CAN\_FreeIrq() is called to sever the interrupt request line between the CAN core and the kernel. Once the interrupts have been disconnected, CAN\_StopChip() is called to take the AIM104-CAN offline. munmap\_device\_io() is called to free the memory mapped device I/O space that was used by the CAN board. can\_close() calls and returns iofunc\_close\_ocb\_default() to ensure that all of the QNX operations initiated in the iofunc\_default\_open() are appropriately handled.

## \_\_LDDK\_READ\_TYPE can\_read(\_\_LDDK\_READ\_PARAM), "can\_read.c"

can\_read() is a device I/O function that retrieves CAN messages from the receive queue. can\_read() prints a message to stderr announcing that it is running before anything else occurs. can\_read() calls iofunc\_read\_verify() to ensure that the CAN device is opened in a manner that permits reading. If iofunc\_read\_verify() returns a failure status, can\_read() exits with an error. This resource manager does not support any special xtypes, so the new read() function checks for xtypes in the message and exits

with an error, if xtypes are being used. Once the precautions have been taken,  $can\_read()$  checks to see if there are any new messages. If no new messages have been placed in the receive queue,  $can\_read()$  replies with a message of zero bytes. If a message is waiting in the receive queue,  $can\_read()$  replies with a message pointing to the dequeued message and sets status flags.  $can\_read()$  returns a value to the calling function that all message replies have already been handled.

#### \_\_LDDK\_WRITE\_TYPE can\_write(\_\_LDDK\_WRITE\_PARAM), "can\_write.c"

can\_write() is a device I/O function that is responsible for sending CAN message using the AIM104-CAN. can\_write()'s first course of action is to print an announcement to stderr indicating that can\_write() is being run. iofunc\_write\_verify() is called to ensure that the CAN device has been opened for writing. If the CAN device is not opened for writing, the function replies with an error message and exits. Otherwise, xtypes are checked for, and if xtypes are being used, can\_write() exits with an error. can\_write() obtains the message to be sent using resmgr\_msgread(). If the message is read correctly, the requested number of bytes is stored in a canmsg\_t structure. If an error occurs while reading the message, can\_write() exits with an error. At this point interrupts are disabled. If no message are waiting in the transmit queue, the message is sent immediately using the CAN\_SendMessage() function. If message are waiting to be transmitted, the current message is enqueued in the transmit queue. Interrupts are enabled; status flags are set; and can\_write() exits with a message indicating that the write has been accomplished.

## \_\_LDDK\_DEVCTL\_TYPE can\_devclt(\_\_LDDK\_DEVCTL\_PARAM), "can\_devctl.c"

can\_devctl() has not been tested; although, the code needed for functionality has

been written.  $can\_devctl()$  allows low level configuration of the AIM104-CAN to be accomplished.  $can\_devctl()$  uses several helper functions that are also contained in "can\_devctl.c". Data structures for  $can\_devctl()$  are defined as types in "can4qnx.h".

## int test\_devctl(resmgr\_context\_t \*ctp, io\_devctl\_t \*msg, RESMGR\_OCB\_T \*ocb), "can resmgr.c"

test\_devctl() is a test function that calls and returns the default

iofunc\_devctl\_default() function that is supplied by QNX. test\_devctl() prints a message

to stderr indicating that it has run.

##

test\_close\_dup() is a test function that calls and returns the default

iofunc\_close\_dup\_default() function that is supplied by QNX. test\_close\_dup() prints a

message to stderr indicating that it has run.

#### can4qnx Resource Manager

## void main(int argc, char \*\*argv), "can\_resmgr.c"

The *main()* function for the can4qnx resource manager handles all the requests for device access. The arguments passed to main are for flags appended to the executable in order to configure the device at the time the resource manager is started. No flags are implemented in the current resource manager. The resource manager's *main()* function prints a message to stderr indicating that it has begun to run. *main()*'s functionality is given in more detail in Chapter Four of this paper.

#### void cleanup\_module(void), "can\_resmgr.c"

cleanup\_module() is a function that disassociates the CAN device's resource manager from the handling threads and path names. Since the operations in this function are synthesized when the resource manager's thread is terminated, this function does not need to be called. In fact, the logistics of calling this function are tedious because the resource manager cannot detach itself, and once the resource manager's thread has been terminated, no thread exists to call cleanup\_module().

#### Miscellaneous Files and Functions

## int Error(int err), "can\_error.c"

Error() is a legacy function held over from can4linux. It simply sets a global variable Can\_errno, also declared in "can\_error.c", to err. Can\_errno's default value is zero. Error() returns a zero upon completion.

#### int Can\_RequestIrq(int irq, void \*handler), "can\_util.c"

Can\_RequestIrq() is a function that attaches handler() to IRQ irq. Since InterruptAttachEvent() is being used in this resource manager, this code is not run. If it were run, interruptID would be assigned the return value from InterruptAttach(). Upon success, IRQ\_requested would be set to one, and Can\_RequestIrq() would return a one. Upon failure, a message is printed to stderr, IRQ\_requested is set to zero, and a zero is returned.

## int Can\_FreeIrq(int irq), "can\_util.c"

Can\_FreeIrq() calls InterruptDetach() to disassociate interruptID from irq.

IRQ\_requested is reset to zero, and the function returns a zero.

## int CanBuf\_Init(canbuf\_t \*mq), "can\_util.c"

CanBuf\_Init() is responsible for initializing the canbuf\_t structure pointed to by mq. CanBuf\_Init() sets the head, tail, and count elements of mq to zero and then returns a zero.

## int CanBuf\_InQ(canbuf\_t \*mq, canmsg\_t \*cm), "can\_util.c"

$CanBuf\_InQ()$  places cm into mq if mq is not full. If mq is full, a "-1" is returned; otherwise,  $CanBuf\_InQ()$  returns a zero.

## int CanBuf\_DeQ(canbuf\_t \*mq, canmsg\_t \*cm), "can\_util.c"

CanBuf\_DeQ() places the next message in mq into the canmsg\_t structure pointed to by cm. If there are no messages in the queue, a "-1" is returned. If a message is placed in mq, a zero is returned.

## int CanBuf\_Count(canbuf\_t \*mq) , "can\_util.c"

*CanBuf\_Count()* simply returns the count element of *mq*.

#### can\_util.c

can\_util.c contains the functions above as well as the receive and transmit queues,Rx\_buff and Tx\_buff, interruptID, and IRQ\_requested.

#### can\_sysctl.c

can\_sysctl.c contains several global variables. IRQ is an int that holds the interrupt used by the CAN device. Base is an int value that holds the base address of the CAN device. Length is an int value that specifies the amount of memory to map to device I/O. Baud is an int value that holds the current baud of the CAN bus. can\_dev is a uintptr\_t variable that holds the pointer to the device's base address. Error counters are also declared and initialized in this file.

#### can\_defs.h

can\_defs.h is a header file for can4qnx. can\_defs.h holds function prototypes for all can4qnx functions. can\_defs.h also defines most global variables as extern to cut down on the number of files that need to be included in program files. Finally, can\_defs.h contains the macros for communicating with the CAN device. These macros are CANin(), CANout(), CANset(), CANreset(), and CANtest().

#### can\_sja1000.h

can\_sja1000.h defines communication tools for use with the SJA1000 chipset. The canregs\_t structure for register access is defined here. can\_sja1000.h also defines bits for each register. Finally, the values for the SJA1000's timing registers are defined here by system clock frequency.

#### can4qnx.h

can4qnx.h defines many of the higher level CAN structures and CAN message bits. The canmsg\_t structure is defined in this file along with flags transmitted in CAN messages. The devctl() structures and flags are also defined in can4qnx.h.

#### APPENDIX B

## Appendix Documenting CCanCore Code

#### CAN Core Class Access Functions

# CCanCore::CCanCore(CInterruptCont \*pIntCont, unsigned long base, unsigned char vector), "ccancore.cxx"

CCanCore() is the constructor for the CCanCore class. When an instance of CCanCore is instantiated, three parameters can be passed to it. pIntCont is a pointer to the interrupt controller class, and must be passed to the instantiation of CCanCore. base is the base address for the CAN core, and defaults to the value of CAN\_BASE defined in "robot2.h". vector is the interrupt vector to use for CAN core interrupts. vector defaults to a value of 17 in the case that it is not passed to the instantiation. CCanCore() sets default values for the CAN core and calls the CCanCore method SetInterruptCont() to set up CAN interrupts.

## CCanCore::~CCanCore(), "ccancore.cxx"

~*CCanCore()* is the destructor for the *CCanCore* class. ~*CCanCore()* is responsible for stopping the CAN core and unregistering the CAN interrupt with the interrupt controller.

## void CCanCore::SetInterruptCont(CInterruptCont \*pIntCont), "ccancore.cxx"

SetInterruptCont() is responsible for registering the CCanCore class with the interrupt controller and unmasking the interrupt. SetInterruptCont() saves the pointer to the interrupt controller in a private variable as well.

#### void CCanCore::GetStat(CanStatusPar\_t \*stat), "ccancore.cxx"

GetStat() returns various CAN core status indicators in the structure pointed to by

stat. The CanStatusPar\_t is defined in "gbaCAN.h".

## int CCanCore::SendMessage(canmsg\_t \*tx), "ccancore.cxx"

SendMessage() is the CCanCore method for transmitting a CAN message.

SendMessage() reads the message from the structure pointed to by tx and puts it on the CAN bus, if the CAN core's transmit buffer is empty. If the transmit buffer has a message waiting to be transmitted, tx is enqueued to the transmit queue. If the transmit buffer is full, the function returns the status of the transmit queue: a "-1" if the queue is full, or a zero if the message was successfully enqueued. If the message is copied to the CAN core's transmit buffer successfully, the SendMessage() returns the number of data bytes copied to the transmit buffer incremented by one.

#### int CCanCore::GetMessage(canmsg\_t \*rx), "ccancore.cxx"

GetMessage() dequeues a message from the receive queue and returns the message in the canmsg\_t structure pointed to by rx. GetMessage() returns the status of the receive queue, namely, a "-1" if the queue is empty and a zero if a message was copied to rx.

## int CCanCore::ChipReset(), "ccancore.cxx"

ChipReset() moves the CAN controller into reset mode and initializes appropriate configuration registers to default values. If the CAN core does not respond to the reset request bit being set in the mode register, the function returns a "-1". Otherwise, ChipReset() clears the status register and sets the clock register, the output control register, the timing characteristics, and the baud for the CAN bus. Note that this controller only supports BasicCAN mode. Upon completion, ChipReset() returns zero.

#### void CCanCore::StartChip(), "ccancore.cxx"

StartChip() moves the CAN controller from reset mode to normal, on bus, operation mode. Before removing the reset request bit, StartChip() releases the receive buffer, clears any overrun status, clears the interrupts, and specifies the events on which to be interrupted.

## void CCanCore::StopChip(), "ccancore.cxx"

*StopChip()* sets the reset request bit in the mode register of the CAN controller.

## void CCanCore::HW\_reset(), "ccancore.cxx"

HW\_reset() resets the CAN controller using the external reset line. Once

HW\_reset() has completed, the CAN core is in the same state it would be in following a hard reset.

#### void CCanCore::SetMask(uint8 code, uint8 mask), "ccancore.cxx"

SetMask() sets the acceptance code and acceptance mask registers of the CAN controller. code is the uint8 value specifying the acceptance code, and mask is the uint8 value specifying the acceptance mask.

#### void CCanCore::SetTiming(int baud) , "ccancore.cxx"

SetTiming() configures the two timing registers on the CAN core. The function switches on baud. If baud matches a baud that has been defined in "gbaCAN.h", the appropriate index is set for the CanTiming array that is initialized in the same file. The indexed values are then written to the timing registers of the CAN core. If baud does not match a predefined value, it is treated as a two 8 bit register values. The upper 8 bits are written to the first timing register, and the lower 8 bits are written to the second timing register. SetTiming() also writes the CAN mode to the clock register. Recall that only BasicCAN is supported. This function returns zero upon completion.

## void CCanCore::SetOMode(int arg) , "ccancore.cxx"

*SetOMode()* writes *arg* to the output control register.

#### int CCanCore::Buf\_InQ(canmsg\_t \*cm, canbuf\_t \*mq), "ccancore.cxx"

$Buf\_InQ()$  is a helper function to ease the enqueuing of CAN message structures from their buffers.  $Buf\_InQ()$  enqueues cm into mq. A zero is returned on success. If the queue is full, a "-1" is returned.